|

【导读】迄今为止用碳纳米管制造的最大的芯片问世了!来自MIT的研究人员制造出一个完全由碳纳米晶体管构成的16位微处理器,包含14000多个碳纳米管(CNT)晶体管。这是新型芯片制造的一个重大里程碑。

《Nature》重大里程碑:史上最大碳纳米管芯片

来源:新智元、Nature

史上最大碳纳米管芯片问世!

今天,来自MIT的Gage Hills等人今天在Nature发表论文,报告了碳纳米管芯片制造领域的一项重大进展:一个完全由碳纳米晶体管构成的16位微处理器。这是迄今为止用碳纳米管制造的最大的计算机芯片。

几十年来,电子技术的进步一直由硅晶体管尺寸的不断缩小而推动。然而,硅晶体管缩小变得越来越困难,现在的收益正在递减。以半导体碳纳米管为基础的晶体管作为先进微电子器件中硅晶体管的替代品,显然很有前景。但碳纳米管固有的纳米级缺陷和可变性,以及处理它们面临的挑战,阻碍了它们在微电子领域的实际应用。

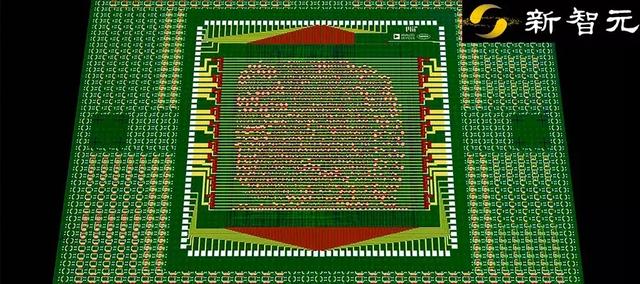

一个完整RV16XNANO裸片的显微图像。处理器核心位于裸片中间,测试电路环绕在外围

作者表示,他们利用14000多个碳纳米管晶体管制造出一个16位微处理器,证明可以完全由碳纳米管场效应晶体管(CNFET)打造超越硅的微处理器,其设计和制造方法克服了之前与碳纳米管相关的挑战,有望为先进微电子装置中的硅带来一种高效能的替代品。

他们将这个处理器命名为RV16X-NANO,这款16位的微处理器基于RISC-V指令集,在16位数据和地址上运行标准的32位指令,包含14000多个互补金属氧化物半导体 CNFET,并使用行业标准的工艺流程进行设计和制造。

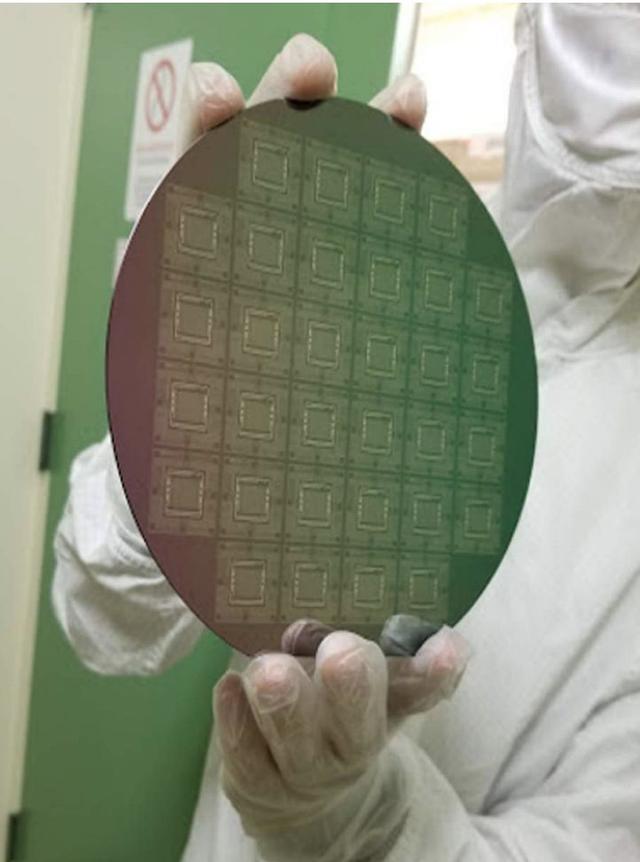

一个完整的RV16X-NANO 150毫米晶圆,每个晶圆包含32个裸片

具体而言,Hills及同事提出一套碳纳米管的制造方法,包括综合处理和设计技术,以克服整个晶圆宏观尺度上的纳米级缺陷。他们利用一种剥落工艺防止碳纳米管聚合在一起,以防晶体管无法正常工作。此外,通过细致的电路设计(减少了金属型碳纳米管而非半导体型碳纳米管的数量,后者的存在不会影响电路的功能),他们还克服了一些和碳纳米管杂质相关的问题。

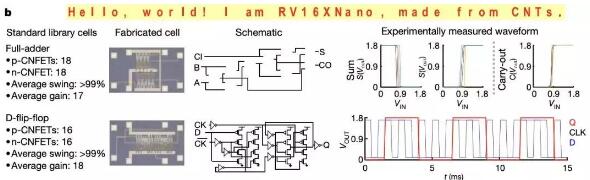

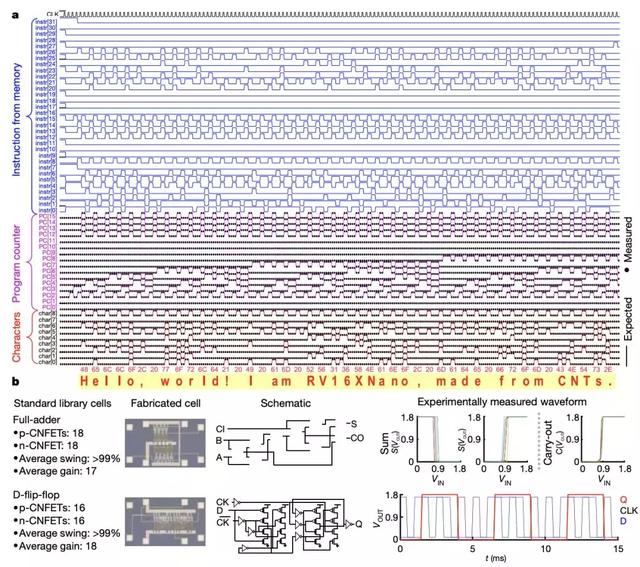

作者将其微处理器命名为“RV16X-NANO”,并在测试中成功执行了一个程序,生成消息:“你好,世界!我是RV16XNano,由碳纳米管制成。”

《Nature》重大里程碑:史上最大碳纳米管芯片

“你好,世界!我是RV16XNano,由碳纳米管制成”

里程碑突破!克服三大缺陷,提出完整碳纳米管制造方法

碳纳米管(Carbon Nanotube ,缩写为 CNT)是一种直径仅为 1 纳米,或十亿分之一米的管状纳米级石墨晶体。几天前在Hot Chips会议上,台积电研发负责人黄汉森(Phillip Wong)在谈到未来要将晶体管将缩小到0.1nm尺度,便提出碳纳米管作为一种使晶体管更快、更小的新技术,正在变得切实可用。

在过去10年中,CNT技术已经得到快速的发展,以往的研究已经实现单个CNFET、单个数字逻辑门,乃至小型的数字电路和系统。2013年,MIT的研究组实现了一个完整的数字系统演示:一个由178个CNFET组成的计算机原型,但它所能做的很有限,只实现了在单个数据位上操作的单条指令。

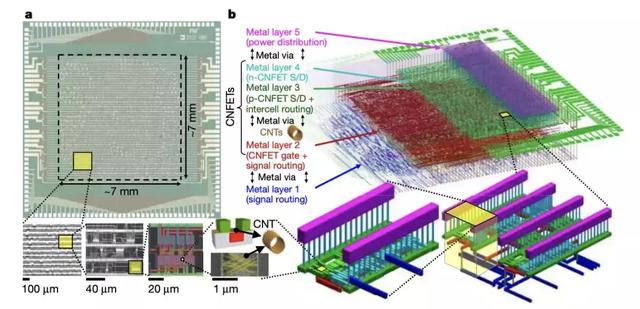

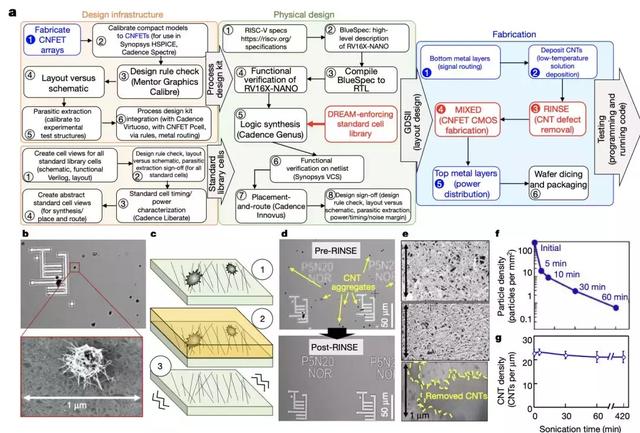

图1:RV16X-NANO。a是制备的RV16X-NANO芯片,裸片面积6.912 mm×6.912 mm

这些小规模的演示与包含数万个(例如微处理器)甚至数十亿个(例如高性能计算服务器) FET的现代系统之间仍然存在很大的脱节。具体到CNT,存在三个内在的挑战:材料缺陷、制造缺陷和可变性。

材料缺陷:由于无法精确控制碳纳米管的直径,导致每次合成的碳纳米管中都含有一定比例的金属CNT,这会导致高泄漏电流和潜在的错误逻辑功能。

制造缺陷:在晶圆制造过程中,CNT天生地“捆绑”在一起,形成厚的CNT聚集体,这会导致CNFET失效(降低CNFET电路成品率),以及超大规模集成电路(VLSI)制造过程中令人望而却步的高颗粒污染率。

可变性:以前实现CNT CMOS的技术要么依赖于极强反应性、非空气稳定、非硅CMOS兼容的材料,要么缺乏可微调性、稳健性和重现性。这严重限制了CNT CMOS的复杂性。

在这项工作中,作者克服了固有的CNT缺陷和变化性,成功制造出超越硅的现代微处理器:RV16X-NANO,其设计和制造完全使用碳纳米管晶体管。

他们提出一套碳纳米管制造方法(manufacturing methodology for CNTs,MMC),将原始的处理和电路设计技术结合起来克服了固有的碳纳米管的挑战。

图4:MMC。RV16X-NANO的设计和制造流程

MMC的关键要素是:

RINSE(removal of incubated nanotubes through selective exfoliation)。提出一种通过选择性机械剥落工艺去除CNT聚集体缺陷的方法。在不影响非聚集CNTs或降低CNFET性能的情况下,RINSE方法可将CNT聚集体缺陷密度降低>250倍。

MIXED (metal interface engineering crossed with electrostatic doping)。所提出的 CNT 掺杂工艺结合了金属接触功函数工程和静电掺杂,可实现稳健的晶圆级 CNFET CMOS 工艺

DREAM (designing resiliency against metallic CNTs)。该技术通过电路设计完全克服了金属碳纳米管的存在。DREAM将对金属CNT纯度的要求放宽了1万倍左右(从半导体CNT纯度要求99.999999%放宽到99.99%),不需要额外的加工步骤或冗余。DREAM是使用标准的电子设计自动化(EDA)工具实现的,成本最低,并使具有CNT纯度的数字VLSI系统可以商用。

更重要的是,整个MMC是晶圆级的,与超大规模集成电路兼容,并且在设计和处理方面与现有的硅集成电路基础设施无缝集成。

具体来说,RV16X-NANO是使用标准EDA工具设计的,并且只利用了与商用硅CMOS制造设施兼容的材料和工艺。

总之,这些贡献构建起强大的CNT CMOS技术,并代表了超越硅的电子发展的一个重要里程碑。

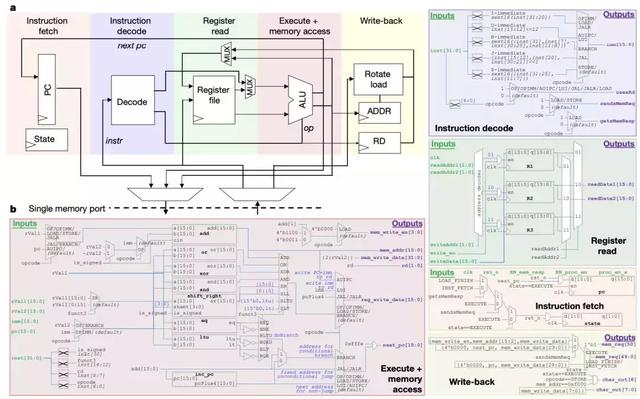

RV16X-NANO的架构和设计

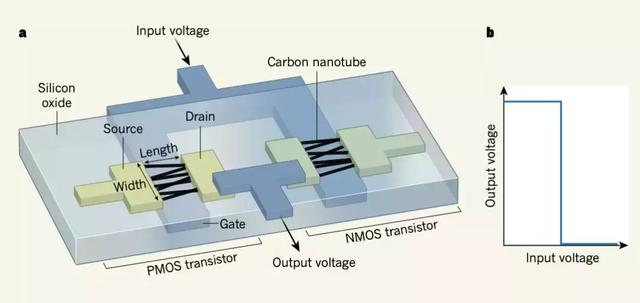

作者开发了一种可行的纳米晶体管技术,提供两种晶体管:p型金属氧化物半导体(PMOS)和n型金属氧化物半导体(NMOS)。在数字电子学中,计算被分成一系列基本(逻辑)操作,这些操作由称为逻辑电路的部件执行。目前电子工业中这些电路的设计是基于互补金属氧化物半导体(CMOS)技术的,需要PMOS和NMOS晶体管。

当一个负(或正)电压被施加到一个称为栅极的电极上时,PMOS(或NMOS)晶体管就被接通。该电极控制两个电极(源极和漏极)之间通道的导电性(在本例中通道由碳纳米管组成)。当一个PMOS晶体管和一个NMOS晶体管串联时,结果是一个称为逆变器(inverter)的元件(如下图所示)。如果对这样的逆变器施加低电压,输出电压就会很高,反之亦然。这个元件是Hills及其同事设计的计算机中所有逻辑电路的基本组成部分。

一个碳纳米管逆变器

作者通过在基板上形成随机分布的高纯度(99.99%)半导体纳米管网络来制作晶体管。它的形成过程类似于将一碗煮熟的意大利面倒在一个表面上,然后将所有不与表面直接接触的面条去除。其结果是基板上覆盖有一层大致是单层的随机取向的纳米管。

图2:RV16X-NANO的架构和设计

然后,Hills等人在纳米管上沉积金属,将它们与源极和漏极连接起来。这种金属的功函数(从表面去除电子所需的能量)取决于该器件是PMOS晶体管还是NMOS晶体管。作者用精心挑选和修剪过的氧化物材料覆盖了每根纳米管的其余部分,以便将纳米管与其周围环境隔离开来,并调整它们的性能。原则上,基板不需要由硅制成;它只需要是平的。此外,加工过程发生在相对较低的温度(约200-325℃),因此可以很容易堆叠其他功能层。

你好,世界!我是RV16XNano,由碳纳米管制成。

现代计算机设计是基于标准单元库的。Hills和他的同事们设计了使用商用传统设计工具来构建计算机架构所必需的所有标准单元。由于半导体纳米管的纯度为99.99%,其中约0.01%是金属(非半导体),可能会危害电路。然而,某些标准单元的组合比其他更容易受到金属纳米管的影响。因此,作者强制执行修改后的设计规则,将这种脆弱的组合排除在外。

有了这些工具,他们就可以通过让计算机执行“Hello, World”(一个在运行时输出“Hello, World”消息的简单程序)来设计、制造和测试他们的处理器了。

图3:RV16X-NANO实验结果。a、实验测量波形来自RV16X-NANO,执行了著名的“Hello, World”程序。

Hills及其同事的碳纳米管处理器基于CMOS技术,在16位数据上运行32位指令,晶体管通道长度约为1.5微米。因此,它可以与基于硅的英特尔80386处理器相比较,后者是1985年推出的,具有类似的规格。早期的80386可以以16兆赫的频率处理指令,而碳纳米管处理器的最大处理频率约为1兆赫。造成这种差异的原因在于电子元件的电容(电荷存储能力),以及最小晶体管所能输出的电流量。

数字逻辑仅仅涉及晶体管栅极和互连进行充电和放电。充电和放电的速度取决于晶体管所能提供的电流的大小,这与晶体管的宽度和长度有关。一个设计良好的硅晶体管可以提供大约宽度每微米1毫安的电流(1 mA µm⁻¹) 。相比之下, Hills 等人使用的典型纳米管晶体管,只能提供大约6µA µm⁻¹。这是该处理器的未来版本主要需要改进的地方。

增加电流的第一步是减小晶体管通道的长度。已经证明纳米管晶体管的通道长度可以缩减到5纳米。第二步是将每个通道的纳米管密度从每微米10个纳米管增加到每微米500个纳米管。

对于这些随机分布的纳米管网络,可实现的密度可能会存在上限,但沉积技术已经被证明能够将这种网络的电流提高到1.7 mA µm⁻¹。

第三步是减小晶体管的宽度,从而减小源极和漏极的宽度,使这些电极能更快地充放电。缩小晶体管尺寸对于以纳米管为基础、以千兆赫频率工作的CMOS技术来说是必不可少的

Hills及其同事的研究成果是基于对每个晶体管通道中几个纳米管性能进行平均。在未来的大规模纳米管计算机中,PMOS和NMOS晶体管将只包含一个纳米管。这些纳米管必须是半导体的:如果逆变器中的两个纳米管中有一个是金属的,那么没有任何设计技巧可以解决这个问题。

这项工作毫无疑问是一个伟大的成就,涉及从材料科学到加工技术、从电路设计到电气测试等许多研究课题。当然,在实现商用之前,还需要更多的努力。

论文链接:https://www.nature.com/articles/s41586-019-1493-8

文章来源:新智元

|